What We Offer?

Solutions for your memory testing business

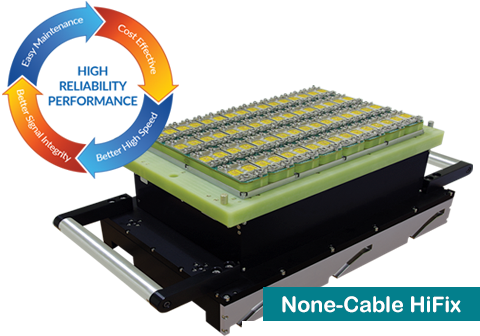

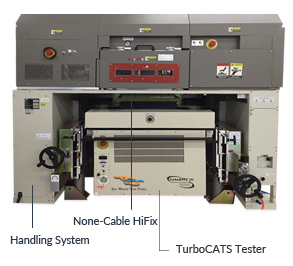

TurboCATS is pioneering a high performing None-Cable HiFix unit integrated with our high performance TCIII-3200STDRIC / TCIII-3200STLPIC NANDFlash IC test system. The tester is connected to the IC socket board via TurboCATS' None-Cable HiFix unit, which is cableless to maximize the performance of the signal transmission. This ensures that the test system is easy to maintain since the user no longer needs to go through hundred of cable wires within the unit.

Customizable Options:

TCIII-3200STDRIC / DDR4 & DDR3

- DDR4 - supports speeds up to 3200Mbps

- DDR3 - supports speeds up to 2133Mbps

TCIII-3200STLPIC / LPDDR4 & LPDDR3

- LPDDR4 - supports speeds up to 3200Mbps

- LPDDR3 - supports speeds up to 1833Mbps

What is None-Cable HiFix?

Speed, signal integrity and costs are the challenges for building a HiFix unit integrated to the automated handler system. The conventional HiFix comes with a large bundle of long cable wires to connect with the HiFix and IC socket boards. It causes signal degradation and timing jitter due to the impedance mismatching, conductor losses, radiation effects, etc. It is also difficult to maintain and repair any problems that need to go through a large bundle of cable wires.

Powerful Integration Tool

Combination of Failures

- Functional Failure: Cell stuck-at, coupling, neighborhood sensitivity and software error faults

- Parametric Failure: (AC) Speed timing vs. Vdd threshold, (DC) Leakage and Idd's

- Hot-Temperature Failure: System high temperature environment

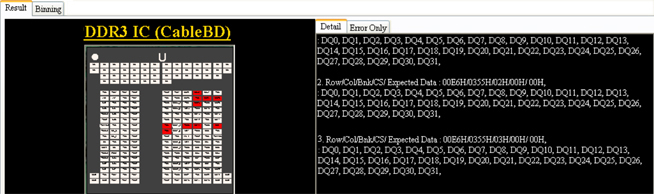

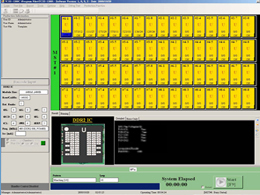

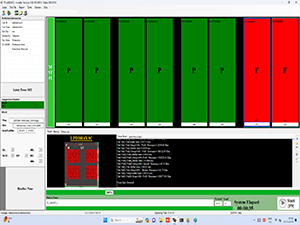

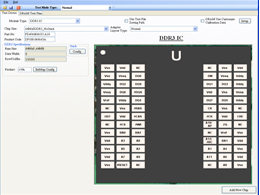

GUI Failure Analysis

Graphical Identification of DQ's

Represents the failed DQ pins locations, graphically. The software uses a graphical picture to show the test failures at the hardware level: If the IC fails during the test, there would be indications (displayed in RED) marking the failed pin(s) and signal(s).

Address / Data Logging

Error logging can analyze failures by using address and data information.

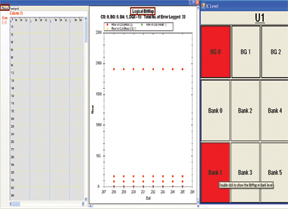

Bit Failure Mapping

A tool that helps the user to find and display the failed DQ bits in the RAM. The corresponding row and column addresses the failed DQ bits, which will be spotted and displayed for the user.

Address Scramble

Address Scramble allows users to redefine an address line logic to the address.

Data Scramble

Data Scramble is based on the input addresses which determines write data or /data.

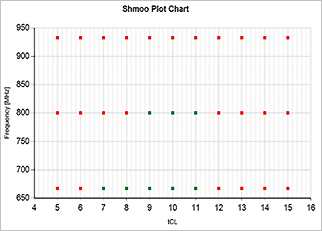

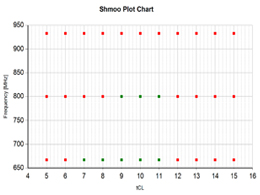

Shmoo Plot

A two-dimensional diagram that shows the status of the DQ bits of Memory ICs varying over a range of the user's selected parameters (timing and input voltage level).

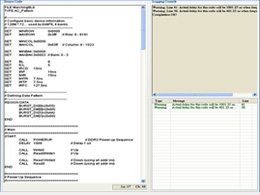

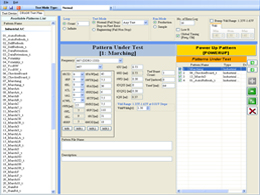

Script Code Function (optional)

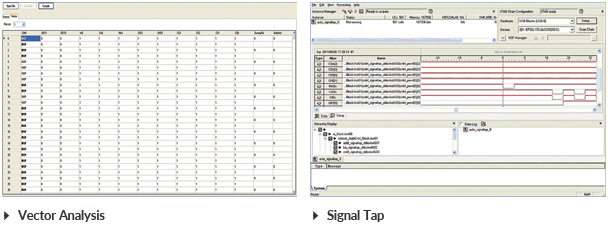

Script Code Debugger

The customer can use a script programming language to create a customized test pattern. It also supports up to maximum 2048 data patterns. The Script Code function also serves as a powerful compiler/debug tool. It contains a built-in compiler and debugger for Script Code programming that allows the user to monitor the timing waveform of the programming algorithm along with the timing bus transactions. This is all accomplished under the Signal Tap tool.

Multi-Site Networking

Solutions for your connected testing

The TCIII-3200STDRIC / TCIII-3200STLPIC multi-site units can be networked so the user can test up to 512 ICs using one PC to control the entire operation. This gives the customer greater flexibility in terms of increasing testing capacity on as need basis. Cost are minimized since there will be no need for additional man labor to handle the increased capacity.

Handler Interface (optional)

Essential Tools

- Supports up to 256 DUTs on DDR4 / DDR3 IC

- Supports up to 128 DUTs on LPDDR4 / LPDDR3 IC

- TurboCATS TCIII-3200IC family supports both manual and automated handler testing

- It can be integrated to various handlers with/ without the None-Cable HiFix

M6771AD / M6741AD Handler

- DDR4/DDR3/LPDDR3 up to 64 DUT's or 128 DUT's

HT-3309 Handler

- LPDDR3 up to 128 DUT's

- DDR3 / DDR4 up to 256 DUT's

Features:

Test Capabilities

TCIII-3200STDRIC - DDR4/DDR3 up to 3200/1866 Mbps

- DDR4 - 1600, 1866, 2133, 2400, 2667, 2866, 2933, 3200 Mbps

- DDR3 - 1333, 1600, 1866 Mbps

- Clock frequency from 667MHz to 1600MHz

TCIII-3200STLPIC - LPDDR4/LPDDR3 up to 3200/1866 Mbps

- LPDDR4 - 1600, 1866, 2133, 2400, 2667, 2866, 2933, 3200 Mbps

- LPDDR3 - 1333, 1600, 1866 Mbps

- Clock frequency from 667MHz to 1600MHz

Flexible Configuration

- Configurable from 6-site to 512-site for parallel testing

- Proper chassis design to meet various selective handlers requirement

- Supports custom load boards for manual test

- Supports None-Cable HiFix for integrating to selective handler interface

- Optional environmental tests from low and high temperatures ranging from -30°C to 125°C

- Optional heat chamber

GUI Failure Analysis Tool

- Failed IC's and DQ's

- Error Logging

- Bit Failure Mapping

- Address/Data Scrambling

- Shmoo Plot

AC & DC Parametric Tests

- Supports ISVM (Contact open pins) and VSIM (Leakage current)

- Supports Continuity, Leakage, Idd's measurement

- Standard test patterns

- User-defined script programming

- Auto timing calibration

Specifications:

| Test Frequency | DDR 3 DDR 4 |

667Mhz to 933Mhz 800Mhz to 1600Mhz |

|

| LPDDR 3 LPDDR 4 |

667MHz to 933MHz 800MHz to 1600MHz |

||

| Switching Data Rate | DDR 3 DDR 4 |

1333Mbps to 1866Mbps 1600Mbps to 3200Mbps |

|

| LPDDR 3 LPDDR 4 |

1333Mbps to 1866Mbps 1600Mbps to 3200Mbps |

||

| I/O Interface | DDR 3 DDR 4 |

SSTL-15, Class I & Class II SSTL-135, Class I & Class II POD12-1.2V Pseudo Open Drain I/O |

|

| LPDDR 3 LPDDR 4 |

1.2V HSUL Supports LVSTL |

||

| Clock Lines | 1 pair per site | ||

| Address Depth | DDR 3 DDR 4 |

16 Rows, 15 Columns, 3 BAs 16X/15Y/3Z per site 18 Rows, 15 Columns, 4 BAs 18X/15Y/4Z per site |

|

| LPDDR 3 LPDDR 4 |

15 Rows, 12 Columns, 3 BAs 15X/12Y/3Z per site 17 Rows, 10 Columns, 3 BAs 17X/10Y/3Z per site |

||

| Data Width | DDR 3 / 4 | Supports x 4 / 8 / 16 / 32 bit IC Device | |

| LPDDR 3 / 4 | Supports x 16 / 32 bit IC Device | ||

| Termination | On-chip, dynamic | ||

| Variable Timing Edges | DDR 3 / 4 | tSU/tHD, tAC(tDS/DH), tDQSS, tWD | |

| LPDDR 3 / 4 | tRCD, tCL, tRL, tWL, tAL, tRP, tRFC, tWR, tCWL, etc. | ||

| Programmable Timing | DDR 3 / 4 | tSU/tHD, tWD, tDQSS, tAC, Tsref, Tref, etc. | |

| LPDDR 3 / 4 | tRCD, tRP, tCCD, tRL, tFAW, tWTR, tRAS, tRTP, tRFC, etc. | ||

| Control PC Requirement | Windows 7 (64 bit) or better, Networking interface | ||

| AC Power Source | 110-240VAC, 50/60Hz | ||

| External PC Requirements (Recommended) |

Executes TCIII-3200IC program to control station operation. Windows 7 (64 bit) operating system or better, i7-core or better, 8G RAM or better, CD DOM, LAN port x 2, USB port, 1920x1080 monitor, keyboard, mouse, display card on board display |

||

TCIII-3200IC with Heat Chamber (optional)

The heat Chamber creates a hot testing environment to simulate the accelerated life testing and analyze the behaviors of the module.

Heat Chamber Specifications:

| Power Supply | 220V, 50Hz (90 - 110% of rated voltage) |

| Power Consumption: | Power-up : 15A, 220V Normal operation : 10A, 220V |

| Display Method | 7 Segment LED Display Processing value (PV) : Green Setting value (SV) : Red |

| Display Accuracy: | F.S ±0.5% rdg ±1 digit based on SV or 3°C Max. |

| Sampling Time | 0.5 sec. fixed |

| Vibration: | 0.75mm amplitude at frequency of 10-55Hz in each of X, Y, Z directions for 2 hours |

| Ambient Temperature | -10 - 50°C |

| Storage Temperature | -20 - 60°C |

| Ambient Humidity | 35 - 85% RH |

| Temperature Range | 25°C - 85°C |

| Recommend Setting Temperature | 80°C |

| Air Input | Min. 0.5 MPa - Max. 1.0 MPa Min. 75 psi - 145 psi |

| Diameter of Gas Tube | 6 mm |

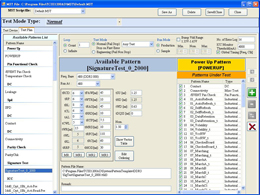

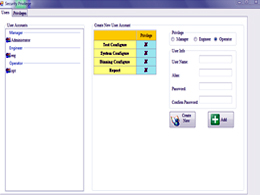

Software Screenshots:

Main Operating Window

Scrip Code Program

Signal Tap Tool

Shmoo Plot

Test Device

Test Plan

Test List

Security Privilege

TURBOCATS, LTD. RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE. Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.